半导体行业新风口的出现,或将进一步扩大ABF载板供需缺口?

就在最近,苹果分析师郭明錤表示:苹果不会在WWDC 2022上发布AR/MR头显及realityOS系统。

究其原因或许在于:由于ABF载板的供应较为紧张,苹果AR/MR头显设备进入市场仍需要一段时间。

其实早在今年年初,郭明錤曾发布报告称:

苹果AR/MR设备采用双ABF载板,每部苹果AR/MR头戴装置将配备由4nm与5nm生产的双CPU,且双CPU均采用ABF载板,运算力领先竞争对手的产品约2–3年。

本次,我们就来一起探究一下:

为什么ABF载板能卡住苹果强大的供应链市场?

开宗明义,定义先行:

ABF全称是:Ajinomoto Build-up Film;中文名:味之素积层膜。

ABF的故事始于1970年代,彼时,食品公司—味之素集团(Ajinomoto)开始探索鲜味调味品生产副产品的应用。

味之素作为全球十大食品企业之一的“百年老店”,它不仅生产赖氨酸,而且苏氨酸、色氨酸的生产量在世界上也都是最大的。

在当时,半导体产业正在飞速发展;尤其是,印刷电路板制造商需要更好的绝缘材料来保持性能:

当时,传统的绝缘材料是液态的绝缘油墨,而味之素集团当时的开发负责人Koji Takeuchi则跳出了油墨材料思维定式,认为薄膜材料才是未来的发展方向。

味之素研发团队发现制作味精时的副产物可以做出拥有极高绝缘性的树脂类合成素材,于是创造出了一种具有高耐用性,低热膨胀性,易于加工和其他重要特征的热固性薄膜,该膜名为ABF。

要了解为什么ABF载板供不应求的第一步:就是知道ABF载板是什么。

众所周知,芯片是每一个电子设备的计算大脑,但要想要准确、高速地将信息传输到各个电子单元,就需要与外部电路进行连接—— 印刷电路板(PCB)就解决了这个问题。

当一块芯片被安装在印刷电路板(PCB)上时,PCB就相当于芯片的底座;

利用PCB上密密麻麻的布线,完成芯片中内外部各个电子元件的链接。

如果说一块芯片是一个“水库”,那么PCB上的布线就是“水库”之间的“河道”。

但是,芯片与PCB之间可以直接链接吗?以ABF载板为代表的“封装基板”又是个什么东西?

之前,芯片与PCB之间多使用“引线框架”连接,也就是简单粗暴地使用金属丝将芯片的引脚与PCB连起来。

目前,芯片的制程早已进入纳米级,而PCB的制程还处于毫米级;

就像溪水东流入海还需要经过江河一样,芯片到PCB也还需要“封装基板”进行中间过渡。

这必然会导致:在芯片的先进封装工艺里,“封装基板”或许将成为焦点。

封装基板就是集成电路产业链封测环节的关键载体,又称IC载板;占封装原材料成本的40-50%。

IC载板不仅为芯片提供支撑、散热和保护作用,同时为芯片与PCB之间提供电子连接;甚至可埋入无源、有源器件以实现一定系统功能。

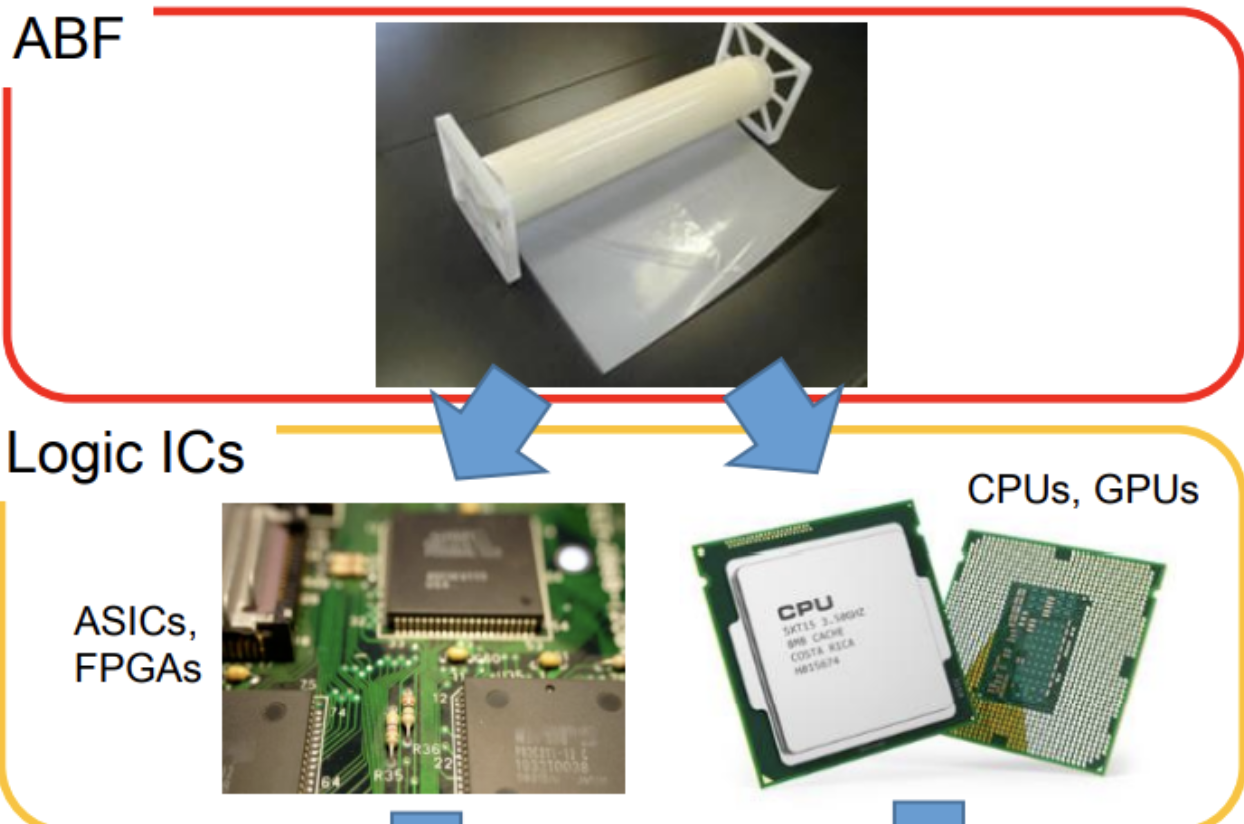

而封装基板的基材,正是用的ABF材料:

通过对ABF板进行蚀刻、镀铜等操作,形成一层又一层的导电图形。

越是制程先进的芯片,电路线宽越小,相应的绝缘材料原有的间隙也变得越小,这时候还需要填充进去,对绝缘材料要求自然很高。

而,使用ABF基材的封装基板,最低可达到5/5微米的线宽/线距,让其无惧于复杂的电气结构!

其中ABF载板主要用于CPU、GPU、FPGA、ASIC等高性能运算IC。

ABF基材匹配半导体先进制程,以满足其细线路、细线宽的要求。

目前,ABF载板已经成为FC-BGA封装的标配。

就在今年年初,知名投资银行高盛就曾声称:

由于高端半导体需求旺盛,ABF载板供应紧张将成新常态。

近年来在5G、AIoT、HPC等应用及Chiplet技术封装趋势带动下,半导体产业链对ABF载板需求大幅提升,开始呈现供不应求态势,价格也持续上扬。

加上“宅经济”、远距离工作等场景推动CPU、GPU等LSI芯片用量倍增,FC-BGA基板需求大增,ABF载板景气上涨。

高盛证券预计ABF载板将在2021年涨价15%的基础上,2022年将再涨10%。

近几年来,以Chiplet技术为代表的先进封装话题,可谓是不绝于耳:

其中, Chiplet 技术的发展将会增大芯片封装面积,提升 ABF 载板用量:

以Chiplet技术为代表的异质异构集成 的核心在于通过先进的封装技术,将不同工艺、不同材质的 chiplets封装在同一个 芯片中,以实现芯片性能、良率的提升和成本的降低;这会导致其集成芯片的尺寸将会更大。

以 AMD 高端 CPU-EPYC 为例:

EPYC 采用 4 个独立 chiplets一起封装的方式,实现了单 CPU 64 核 128 线程的设计目标。EPYC 最终的封装面积为 852 平方毫米,是单个 Die 封装面积的 4 倍。

可预见的是:Chiplet技术在提升芯片性能的同时,也大大增加了对载板材料的消耗。

该类技术渗透率的提升亦将进一步提升市场对 ABF 载板的需求。

针对这个问题,或许我们可以探索一个新的技术手段去解决Chiplet技术对ABF载板材料消耗问题:

我们以台积电的CoWoS2.5D封装技术为例:

CoWoS 技术概念,简单来说是先将Die,一同放在硅中介层上,再透过Chip on Wafer(CoW)的封装制程连接至底层基板上。

利用这种封装模式,使得多颗芯片可以封装到一起,透过封装基板互联,达到了封装体积小,功耗低,引脚少的效果;从而间接性地减少了对ABF载板的依赖。

我们在此可以展开一个这样的畅想:

或许在不久以后的未来,以2.5D封装技术为代表的Chiplet技术中使用的封装基板,或将承载更多的功能;

从而大大减少相关芯片对于载板的消耗,使相关成本得以降低。

本次 ABF载板 我们就先讲到这儿~

想了解更多半导体行业动态,请您持续关注我们。

奇普乐®️将在每周,不定时更新~

最后的最后,借由李四光的名言:

科学的存在全靠它的新发现,如果没有新发现科学便死了。

愿每一位半导体从业者可以——

基于心,研与行!